I

| Name         |            |

|--------------|------------|

| Roll No.     | Year 20 20 |

| Exam Seat No |            |

ELECTRONICS GROUP SEMESTER - VI DIPLOMA IN ENGINEERING AND TECHNOLOGY

# A LABORATORY MANUAL FOR

## **Very Large Scale Integration**

with VHDL (22062)

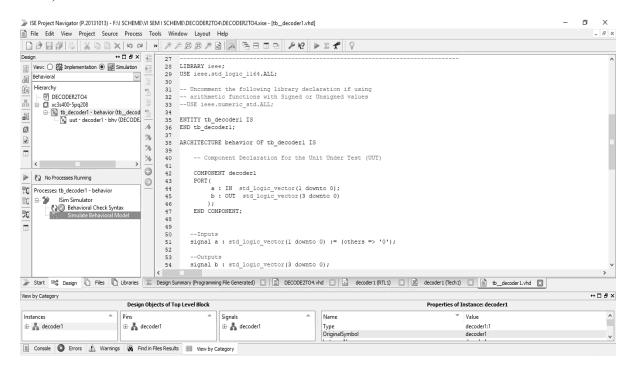

(EJ)

MAHARASHTRA STATE BOARD OF TECHNICAL EDUCATION, MUMBAI (Autonomous) (ISO 9001 : 2015) (ISO / IEC 27001 : 2013)

### **A Laboratory Manual for**

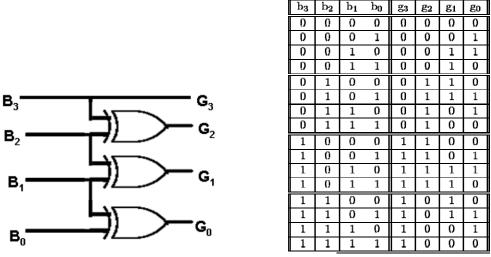

# Very Large Scale Integration with VHDL

(22062)

**Semester-VI**

**(EJ)**

## Maharashtra State Board of Technical Education, Mumbai

(Autonomous) (ISO-9001-2015) (ISO/IEC 27001:2013)

## Maharashtra State Board of Technical Education, Mumbai

(Autonomous) (ISO-9001-2015) (ISO/IEC 27001:2013)

4<sup>th</sup> Floor, Government Polytechnic Building, 49, Kherwadi,

Bandra (East), Mumbai – 400051.

(Printed on November 2019)

## Maharashtra State Board of Technical Education

## Certificate

| This is to certify that Mr | . / Ms                |                         |

|----------------------------|-----------------------|-------------------------|

| Roll No                    | of                    | . Semester of Diploma   |

| in                         |                       | of Institute            |

|                            |                       | (Code)                  |

| has attained pre-defined   | practical outcome     | es(PROs) satisfactorily |

| in course VLSI with V      | WHDL (22062) 1        | for the academic year   |

| 20to 20 as pre             | scribed in the curr   | iculum.                 |

|                            |                       |                         |

| Place                      | Enrollment            | No                      |

| Date:                      | Exam Seat             | No                      |

| Community of the second    | Hard Male Dance       | Detected                |

| Course Teacher             | Head of the Depart    | ment Principal          |

|                            | Seal of the Institute |                         |

#### **Preface**

The primary focus of any engineering laboratory/ field work in the technical education system is to develop the much needed industry relevant competencies and skills. With this in view, MSBTE embarked on this innovative \_I' Scheme curricula for engineering diploma programme with outcome-base education as the focus and accordingly, relatively large amount of time is allotted for the practical work. This displays the great importance of laboratory work making each teacher; instructor and student to realize that every minute of the laboratory time need to be effectively utilized to develop these outcomes, rather than doing other mundane activities. Therefore, for the successful implementation of this outcome-based curriculum, every practical has been designed to serve as a 'vehicle' to develop this industry identified competency in every student. The practical skills are difficult to develop through \_chalk and duster' activity in the classroom situation. Accordingly, the \_I' scheme laboratory manual development team designed the practical's to focus on the outcomes, rather than the traditional age old practice of conducting practical's to verify the theory' (which may become a byproduct along the way).

This laboratory manual is designed to help all stakeholders, especially the students, teachers and instructors to develop in the student the pre-determined outcomes. It is expected from each student that at least a day in advance, they have to thoroughly read through the concerned practical procedure that they will do the next day and understand the minimum theoretical background associated with the practical. Every practical in this manual begins by identifying the competency, industry relevant skills, course outcomes and practical outcomes which serve as a key focal point for doing the practical. The students will then become aware about the skills they will achieve through procedure shown there and necessary precautions to be taken, which will help them to apply in solving real-world problems in their professional life.

This manual also provides guidelines to teachers and instructors to effectively facilitate student-centered lab activities through each practical exercise by arranging and managing necessary resources in order that the students follow the procedures and precautions systematically ensuring the achievement of outcomes in the students.

In the present scenario of electronics technology, CMOS is a vital important and basic need in the design/development of almost all products in the range from consumer to industrial and telecommunication engineering area. Functional capabilities of this technology leads to advanced Very Large Scale Integration, large density of components, high speed of operation, less area with less power dissipation. Therefore imparting knowledge of VLSI and its tools is need of today. After completion of this course, students will be able to develop applications in the area of digital electronics using VLSI design tools.

Although all care has been taken to check for mistakes in this laboratory manual, yet it is impossible to claim perfection especially as this is the first edition. Any such errors and suggestions for improvement can be brought to our notice and are highly welcome

## Programme Outcomes (POs) to be achieved through Practical of this Course

Following programme outcomes are expected to be achieved through the practical of the course.

- PO1. **Basic knowledge:** Apply knowledge of basic mathematics, sciences and basic engineering to solve the broad-based Electronics and Telecommunication engineering problems.

- PO2. **Discipline knowledge:** Apply Electronics and Telecommunication engineering knowledge to solve broad-based Electronics and Telecommunications engineering related problems

- PO3. **Experiments and practice:** Experiments and practice: Plan to perform experiments and practices to use the results to solve broad-based Electronics and Telecommunication engineering problems

- PO4. **Engineering tools:** Apply relevant Electronics and Telecommunications technologies and tools with an understanding of the limitations

- PO5. **The engineer and society:** Assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to practice in field of Electronics and Telecommunication engineering

- PO6. **Environment and sustainability:** Apply Electronics and Telecommunication engineering solutions also for sustainable development practices in societal and environmental contexts

- PO7. **Ethics:** Apply ethical principles for commitment to professional ethics, responsibilities and norms of the practice also in the field of Electronics and Telecommunication engineering.

- PO8. **Individual and team work:** Function effectively as a leader and team member in diverse/ multidisciplinary teams

- PO9. Communication: Communicate effectively in oral and written form

- PO10. **Life-long learning:** Engage in independent and life-long learning activities in the context of technological changes also in the Electronics and Telecommunication engineering and allied industry.

- **Program Specific Outcomes (PSO)** (What s/he will be able to do in the Electronics and Telecommunication engineering specific industry soon after the diploma programme)

- **PSO1. Electronics and Telecommunication Systems:** Maintain various types of Electronics and Telecommunication systems.

- **PSO2. EDA** Tools Usage: Use EDA tools to develop simple Electronics and Telecommunication engineering related circuits.

#### **Practical- Course Outcome matrix**

#### **Course Outcomes (COs)**

- a. Develop design flow for the given application using VLSI tools.

- b. Interpret CMOS technology circuits with their specifications.

- c. Use relevant VHDL model for given application.

- d. Debug VHDL programme for the given application.

- e. Maintain FPGA based circuits

| Pro.<br>No. |                                                                                 |   | CO       | СО       | СО       | СО       |

|-------------|---------------------------------------------------------------------------------|---|----------|----------|----------|----------|

| 110.        |                                                                                 |   | b.       | c.       | d.       | e.       |

| 1.*         | Identify internal block and pin configuration of FPGA and CPLD using datasheet. |   | -        | -        | -        | -        |

| 2.*         | Develop flow chart of CMOS IC fabrication using relevant website.               | - | <b>√</b> | -        | -        | -        |

| 3.*         | Install EDA tool (VHDL) for VLSI application.                                   | - | -        | <b>✓</b> | -        | 1        |

| 4.*         | Implement any two gates using Data flow and Behavioral model.                   | - | -        | -        | ✓        | -        |

| 5.          | Implement Half/full adder / subtractor using FPGA.                              | - | -        | -        | <b>√</b> | -        |

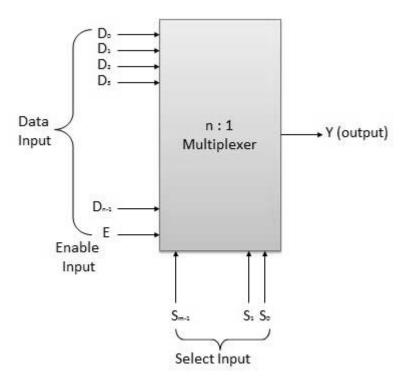

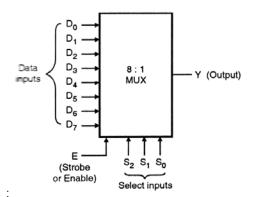

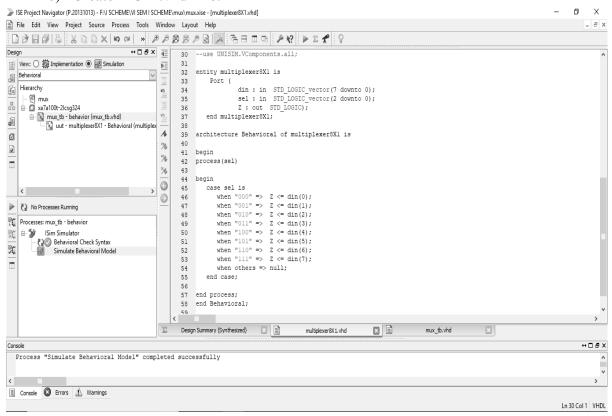

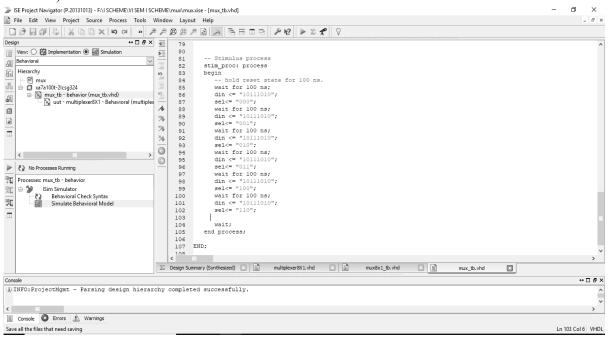

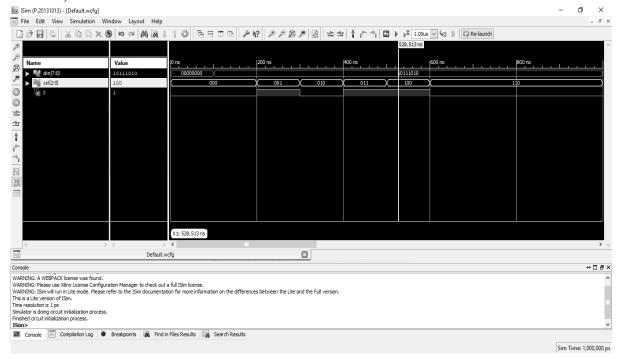

| 6.          | Implement 8:1 multiplexer using FPGA.                                           | - | -        | -        | <b>✓</b> | -        |

| 7.          | Implement 1:8 Demultiplexer using FPGA.                                         | - | -        | -        | <b>✓</b> | -        |

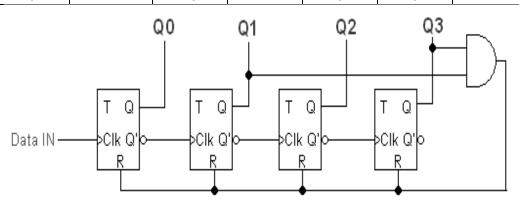

| 8.          | Implement T and D-flip-flop using FPGA.                                         | - | -        | -        | <b>√</b> | -        |

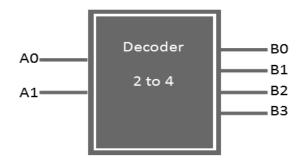

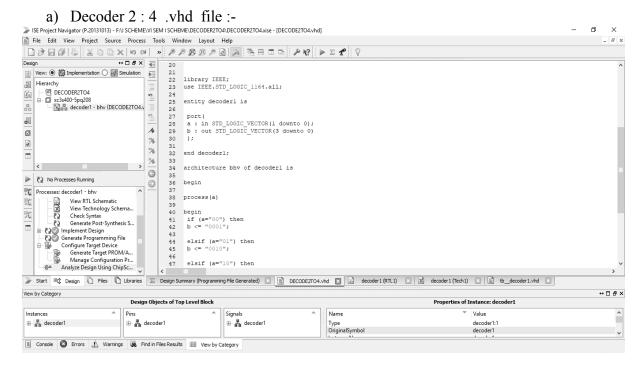

| 9.          | Implement 2:4 Decoder using FPGA.                                               | - | -        | -        | <b>√</b> | -        |

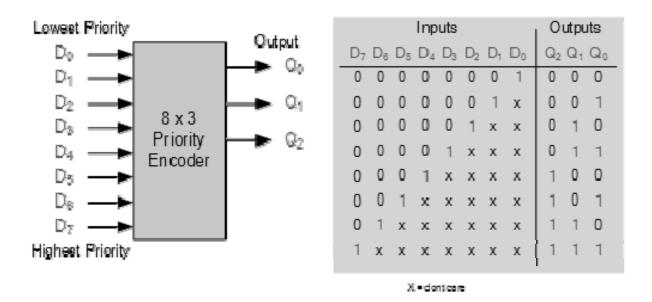

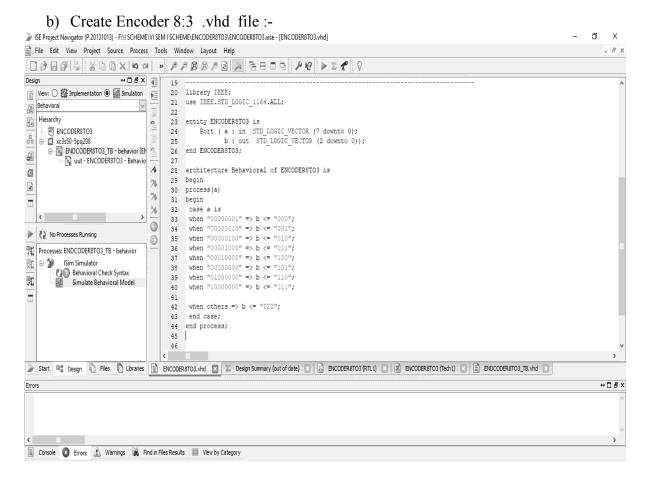

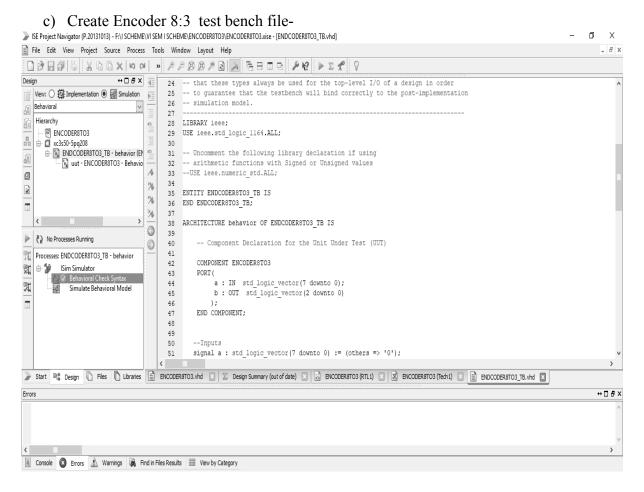

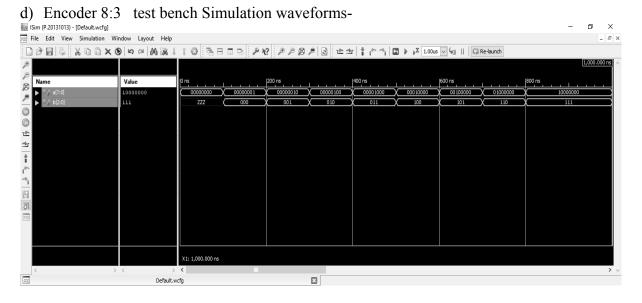

| 10.         | Implement 8:3 Encoder using FPGA.                                               | - | -        | -        | <b>√</b> | -        |

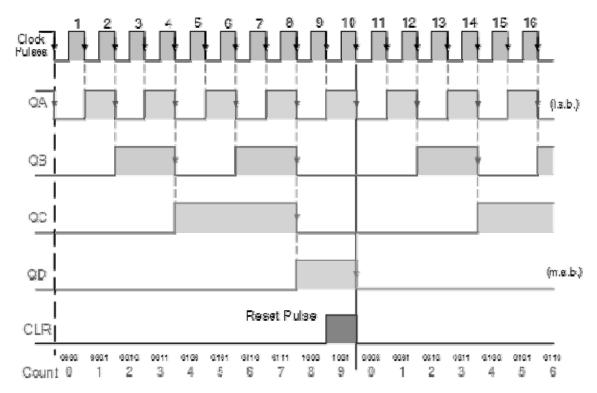

| 11.         | Implement up-counter using FPGA.                                                | - | -        | -        | <b>✓</b> | -        |

| 12.         | Implement synchronous counter using FPGA.                                       | - | -        | -        | <b>✓</b> | -        |

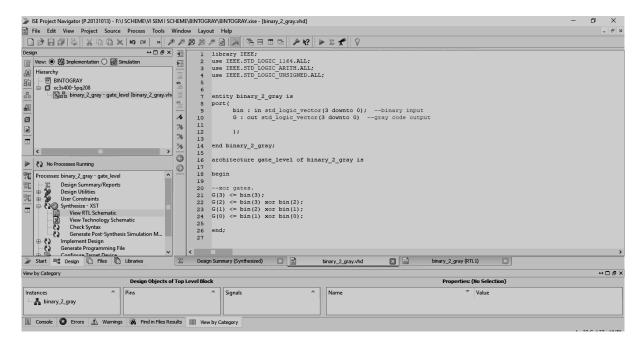

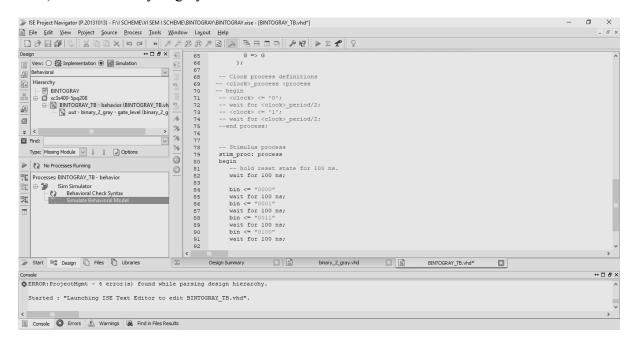

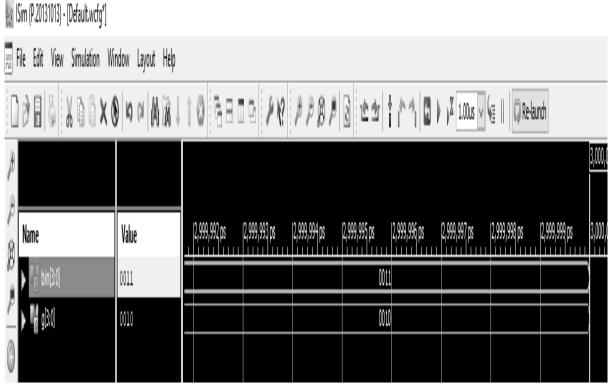

| 13.         | Implement binary to gray code converter using FPGA.                             |   | -        | -        | <b>✓</b> | -        |

| 14.*        | Build /Test DAC using FPGA                                                      |   | -        | -        | -        | <b>√</b> |

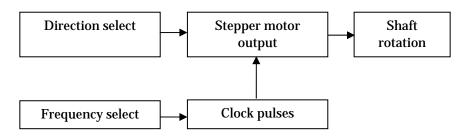

| 15.         | Implement Stepper motor controller using FPGA.                                  | - | -        | -        | -        | <b>√</b> |

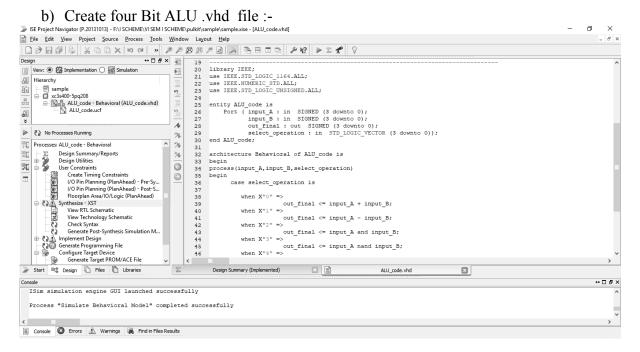

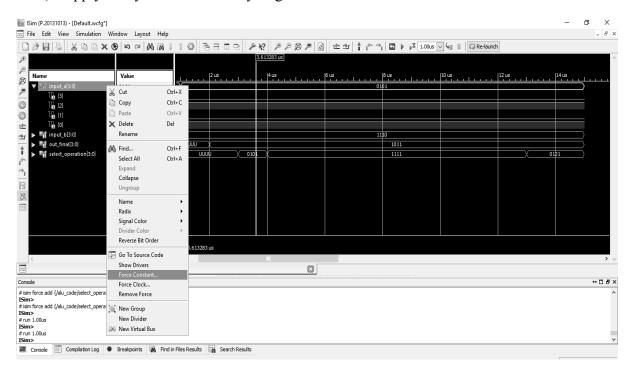

| 16.*        | Implement four Bit ALU or sequence generator using FPGA.                        | - | -        | -        | -        | <b>√</b> |

#### List of Industry Relevant Skills

The following industry relevant skills of the competency 'Maintain VLSI based electronic circuits and equipments' are expected to be developed in students by undertaking the practical's of this laboratory manual.

- 1. Develop the flow chart for CMOS fabrication.

- 2. Identify the various blocks of FPGA and CPLD.

- 3. Develop 'VHDL' code using IDE tools.

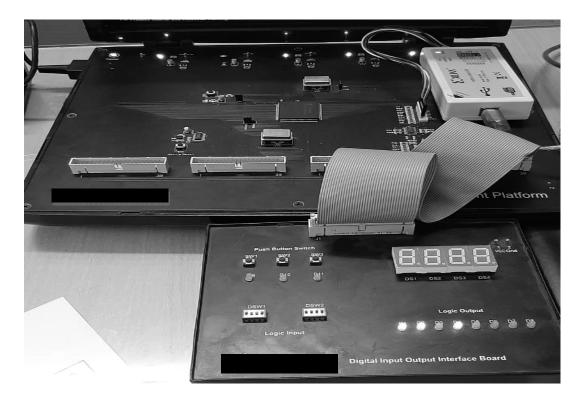

- 4. Use Input/output port pins of FPGA.

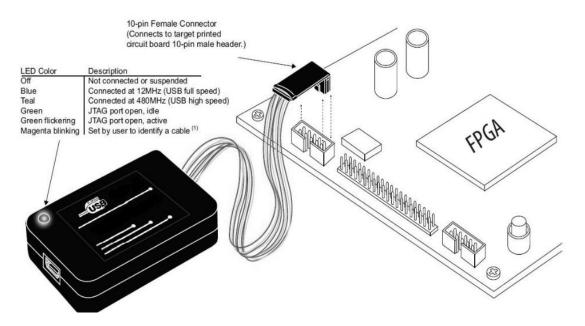

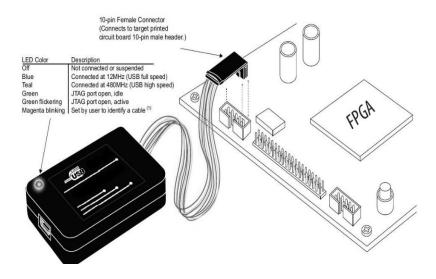

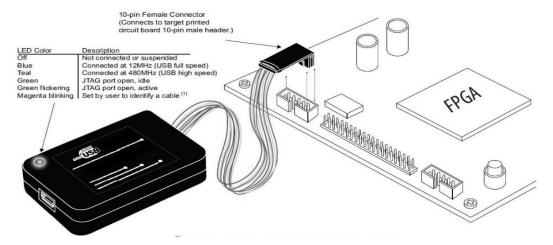

- 5. Interface FPGA KIT and desktop PC.

#### **Guidelines to Teachers**

- 1. Teacher is expected to refer complete curriculum document and follow guidelines for implementation

- 2. Teacher should provide the guideline with demonstration of practical to the students with all features.

- 3. Teacher shall explain prior concepts to the students before starting of each practical

- 4. Involve students in performance of each practical.

- 5. Teacher should ensure that the respective skills and competencies are developed in the students after the completion of the practical exercise.

- 6. Teachers should give opportunity to students for hands on experience after the demonstration.

- 7. Teacher is expected to share the skills and competencies to be developed in the students.

- 8. Teacher may provide additional knowledge and skills to the students even though not covered in the manual but are expected the students by the industry.

- 9. Give practical assignment and assess the performance of students based on task assigned to check whether it is as per the instructions.

- 10. Assess the skill achievement of the students and COs of each unit.

- 11. At the beginning Teacher should make the students acquainted with any of the simulation software environment as few experiments are based on simulation.

- 12. It is desirable to paste the photo of actual practical setup or draw block diagram of practical setup.

- 13. Practical No.1, 2 and 3 should not be consider for Practical (ESE-End Semester Exam).

#### **Instructions for Students**

- 1. Listen carefully the lecture given by teacher about course, curriculum, learning structure, skills to be developed.

- 2. Before performing the practical student shall read lab manual of related practical to be conducted.

- 3. For incidental writing on the day of each practical session every student should maintain a *dated log book* for the whole semester, apart from this laboratory manual which s/he has to *submit for assessment to the teacher*.

- 4. Organize the work in the group and make record of all observations.

- 5. Students shall develop maintenance skill as expected by industries.

- 6. Student shall attempt to develop related hand-on skills and gain confidence.

- 7. Student shall develop the habits of evolving more ideas, innovations, skills etc. those included in scope of manual

- 8. Student shall refer technical magazines, IS codes and data books.

- 9. Student should develop habit to submit the practical on date and time.

- 10. Student should well prepare while submitting write-up of exercise.

**Content** List of Practical's and Progressive Assessment Sheet

| Sr.<br>No. | Title of the practical                                                           | Page<br>No. | Date of performance | Date of submission | Assessment<br>marks(25) | Dated sign.<br>of teacher | Remarks<br>(if any) |

|------------|----------------------------------------------------------------------------------|-------------|---------------------|--------------------|-------------------------|---------------------------|---------------------|

| 1.*        | Identify internal block and pin configuration of FPGA and CPLD using data sheet. | 1           |                     |                    |                         |                           |                     |

| 2.*        | Develop flow chart of CMOS IC fabrication using relevant website.                | 12          |                     |                    |                         |                           |                     |

| 3.*        | Install EDA tool (VHDL) for VLSI application.                                    | 21          |                     |                    |                         |                           |                     |

| 4.*        | Implement any two gates using Data flow and Behavioral model.                    | 31          |                     |                    |                         |                           |                     |

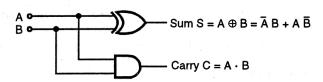

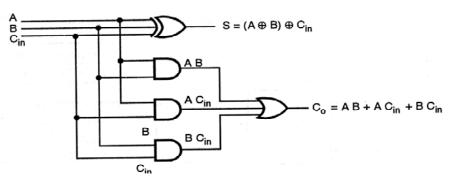

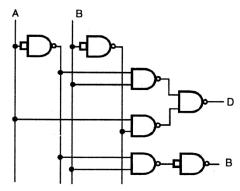

| 5.         | Implement Half /full adder / subtractor using FPGA.                              | 49          |                     |                    |                         |                           |                     |

| 6.         | Implement 8:1 multiplexer using FPGA.                                            | 62          |                     |                    |                         |                           |                     |

| 7.         | Implement 1:8 Demultiplexer using FPGA.                                          | 74          |                     |                    |                         |                           |                     |

| 8.         | Implement T and D-flip-flop using FPGA.                                          | 86          |                     |                    |                         |                           |                     |

| 9.         | Implement 2:4 Decoder using FPGA.                                                | 98          |                     |                    |                         |                           |                     |

| 10.        | 10. Implement 8:3 Encoder using FPGA.                                            |             |                     |                    |                         |                           |                     |

| 11.        | Implement up-counter using FPGA.                                                 | 123         |                     |                    |                         |                           |                     |

| 12.        | Implement synchronous counter using FPGA.                                        | 137         |                     |                    |                         |                           |                     |

| 13.        | Implement binary to gray code converter using FPGA.                              | 151         |                     |                    |                         |                           |                     |

| 14.*       | Build /Test DAC using FPGA                                                       | 164         |                     |                    |                         |                           |                     |

| 15.        | Implement Stepper motor controller using FPGA.                                   | 176         |                     |                    |                         |                           |                     |

| 16.*       | Implement four Bit ALU or sequence generator using FPGA.                         | 190         |                     |                    |                         |                           |                     |

|            | TOTAL                                                                            | •           |                     |                    |                         | •                         | -                   |

- The practical marked as '\*' are compulsory, Column 6<sup>th</sup> marks to be transferred to Performa of CIAAN-2017.

## Practical No. 01: Identify internal block and pin configuration of FPGA and CPLD using data sheet.

#### I Practical Significance

A field-programmable gate array (FPGA) is a regular structure of logic cells (or modules) and interconnect, which is under user's complete control. This allows the user to design, program and make changes to their circuit as per the application. CPLD is "Complex programmable logic devices", is an integrated circuit that application designers design to implement digital hardware like mobile phones. This practical will help the student to identify various blocks and pin configuration of FPGA and CPLD.

#### II Relevant Program Outcomes (POs)

- **Discipline knowledge:** Apply Electronics and Telecommunication engineering knowledge to solve broad-based Electronics and Telecommunications engineering related problems.

- **Experiments and practice:** Plan to perform experiments and practices to use the results to solve broad-based Electronics and Telecommunication engineering problems.

- **Engineering tools:** Apply relevant Electronics and Telecommunications technologies and tools with an understanding of the limitations.

- **Lifelong learning:** Engage in independent and life-long learning activities in the context of technological changes also in the Electronics and Telecommunication engineering and allied industry

#### III Competency and Practical Skills

This practical is expected to develop the following skills for the industry-identified competency: 'Maintain VLSI based electronic circuits and equipments.'

- Identify the various blocks of FPGA and CPLD.

- Understand the architecture of FPGA and CPLD.

- Understand the significance of pins and their use.

#### **IV** Relevant Course Outcome

Develop design flow for the given application using VLSI tools.

#### V Practical Outcome

Identify internal block and pin configuration of FPGA and CPLD using data sheet..

#### VI Relevant Affective domain related Outcome(s)

- Follow safety practices.

- Maintain tools and equipment.

- Follow ethical practices.

#### VII Minimum Theoretical Background

a) Field-programmable gate array (FPGA): A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence "field-programmable". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC) (circuit diagrams were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare).

FPGAs contain programmable logic components called "logic blocks", and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together" – somewhat like many logic gates that can be inter-wired in different configurations. Logic blocks can be conFig.d to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory, ref fig.. no. 1.1.

Fig 1.1 Block diagram of FPGA

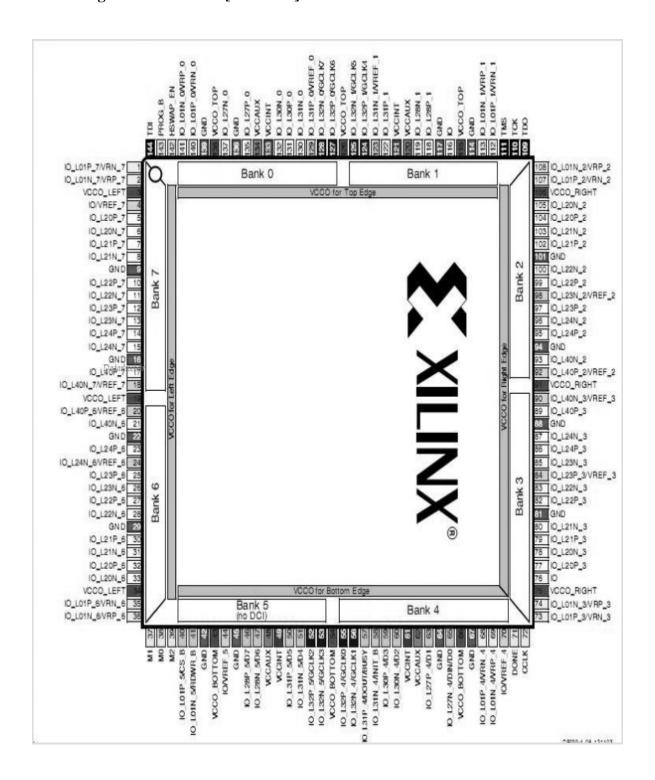

#### Pin Configuration of FPGA [XC3S400]:

Fig 1.2 Pin Diagram of XC3S400

Table 1.1: Pin functions of XC3S400

|        | Table 1.1: Pin functions of XC3S400                                                                                                                                                                                                                                                               |                                                                                                                                                                                             |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type   | Description                                                                                                                                                                                                                                                                                       | Pin Name(s) in Type                                                                                                                                                                         |

| I/O    | Unrestricted, general-purpose user-I/O pin. Most pins can be paired together to form differential I/Os.                                                                                                                                                                                           | IO,<br>IO_Lxxy_#                                                                                                                                                                            |

| DUAL   | Dual-purpose pin used in some configuration modes during the configuration process and then usually available as a user I/O after configuration. If the pin is not used during configuration, this pin behaves as an I/O-type pin. There are 12 dual-purpose configuration pins on every package. | IO_Lxxy_#/DIN/D0, IO_Lxxy_#/D1, IO_Lxxy_#/D2, IO_Lxxy_#/D3, IO_Lxxy_#/D4, IO_Lxxy_#/D5, IO_Lxxy_#/D6, IO_Lxxy_#/D7, IO_Lxxy_#/CS_B, IO_Lxxy_#/RDWR_B, IO_Lxxy_#/BUSY/DOUT, IO_Lxxy_#/INIT_B |

| CONFIG | Dedicated configuration pin. Not available as a user-I/O pin. Every package has seven dedicated configuration pins. These pins are powered by VCCAUX.                                                                                                                                             | CCLK, DONE, M2, M1, M0, PROG_B, HSWAP_EN                                                                                                                                                    |

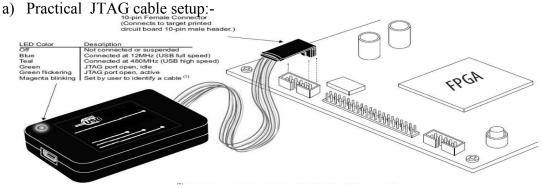

| JTAG   | Dedicated JTAG pin. Not available as a user-I/O pin. Every package has four dedicated JTAG pins. These pins are powered by VCCAUX.                                                                                                                                                                | TDI, TMS, TCK, TDO                                                                                                                                                                          |

| DCI    | Dual-purpose pin that is either a user-I/O pin or used to calibrate output buffer impedance for a specific bank using Digital Controlled Impedance (DCI). There are two DCI pins per I/O bank.                                                                                                    | IO/VRN_# IO_L xxy_ #/VR N_# IO/V RP_# IO_Lxxy_#/VRP_#                                                                                                                                       |

| VREF   | Dual-purpose pin that is either a user-I/O pin or, along with all other VREF pins in the same bank, provides a reference voltage input for certain I/O standards. If used for a reference voltage within a bank, all VREF pins within the bank must be connected.                                 | IO/VREF_# IO_Lxxy_#/VREF_#                                                                                                                                                                  |

| GND    | Dedicated ground pin. The number of GND pins depends on the package used. All must be connected.                                                                                                                                                                                                  | GND                                                                                                                                                                                         |

| VCCAUX | Dedicated auxiliary power supply pin. The number of VCCAUX pins depends on the package used. All must be connected to +2.5V.                                                                                                                                                                      | VCCAUX                                                                                                                                                                                      |

| VCCINT | Dedicated internal core logic power supply                                                                                                                                                                                                                                                        | VCCINT                                                                                                                                                                                      |

| Type | Description                                                                                                                                                                                                                     | Pin Name(s) in Type                                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|      | pin. The number of VCCINT pins depends on the package used. All must be connected to +1.2V.                                                                                                                                     |                                                                                                                                        |

| VCCO | Dedicated I/O bank, output buffer power supply pin. Along with other VCCO pins in the same bank, this pin supplies power to the output buffers within the I/O bank and sets the input threshold voltage for some I/O standards. | VCCO_# TQ144 Package Only: VCCO_LEFT, VCCO_TOP, VCCO_RIGHT, VCCO_BOTTOM                                                                |

| GCLK | Dual-purpose pin that is either a user-I/O pin or an input to a specific global buffer input. Every package has eight dedicated GCLK pins.                                                                                      | IO_Lxxy_#/GCLK0, IO_Lxxy_#/GCLK1, IO_Lxxy_#/GCLK2, IO_Lxxy_#/GCLK3, IO_Lxxy_#/GCLK4, IO_Lxxy_#/GCLK5, IO_Lxxy_#/GCLK6, IO_Lxxy_#/GCLK7 |

| N.C. | This package pin is not connected in this specific device/package combination but may be connected in larger devices in the same package.                                                                                       | N.C.                                                                                                                                   |

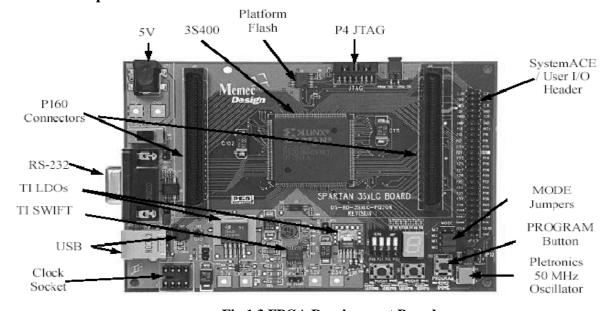

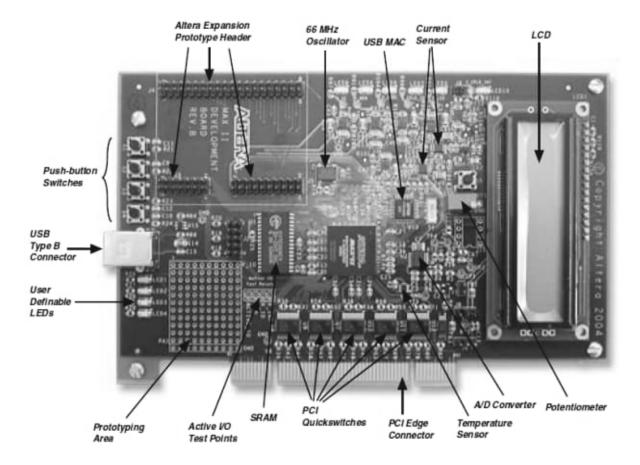

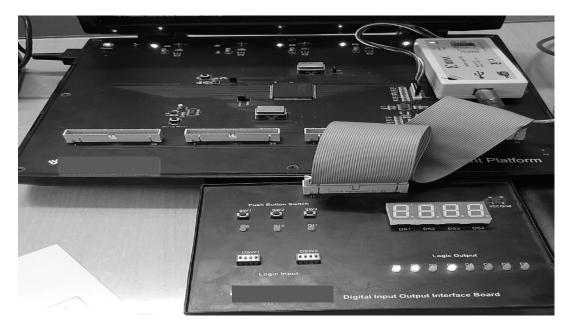

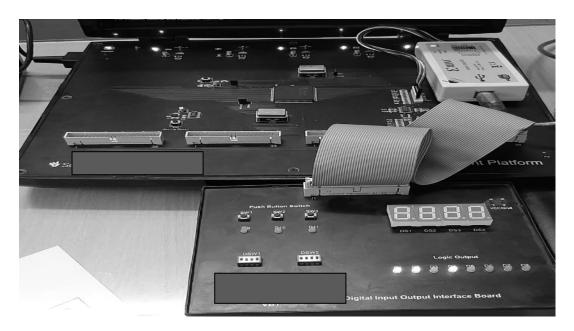

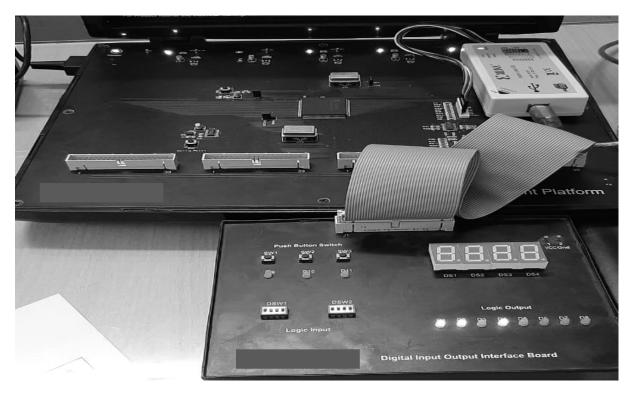

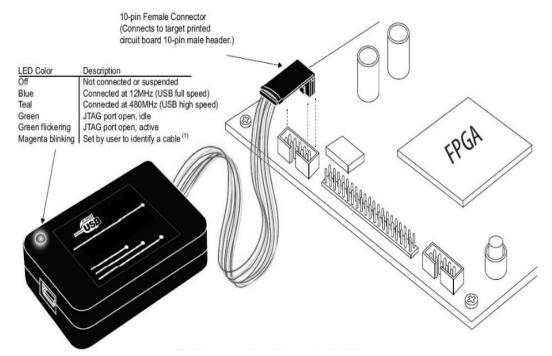

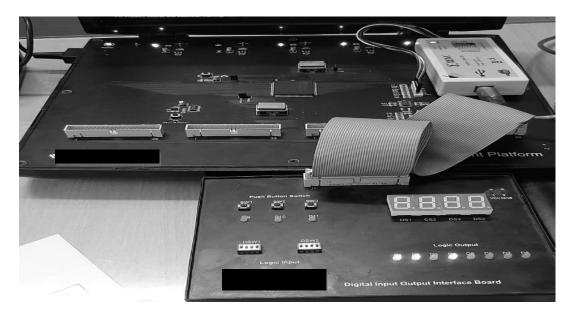

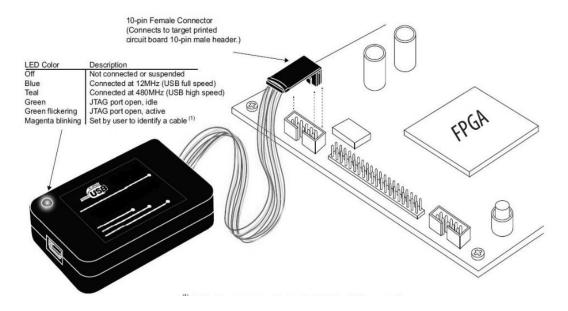

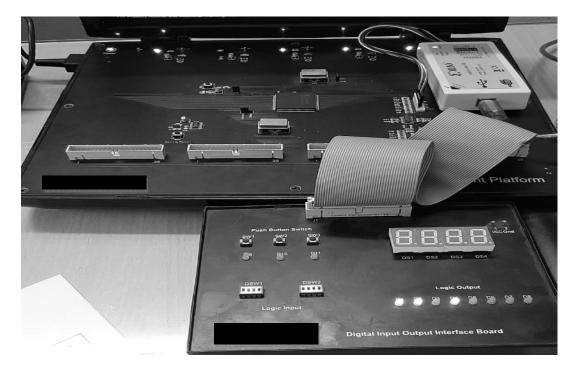

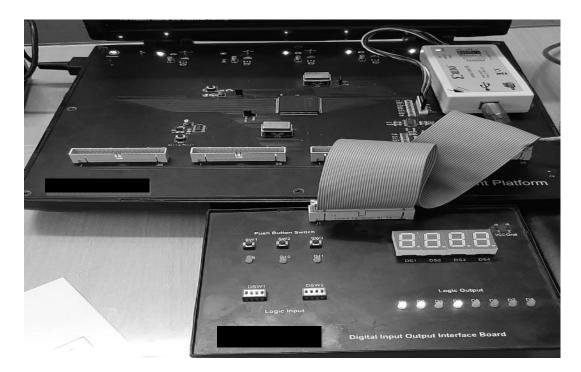

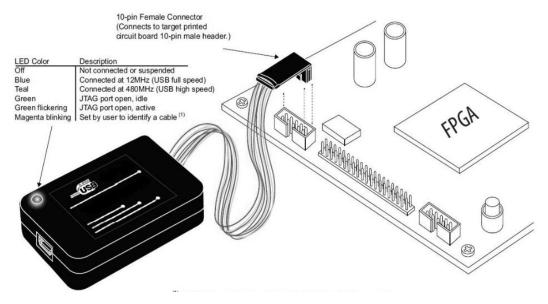

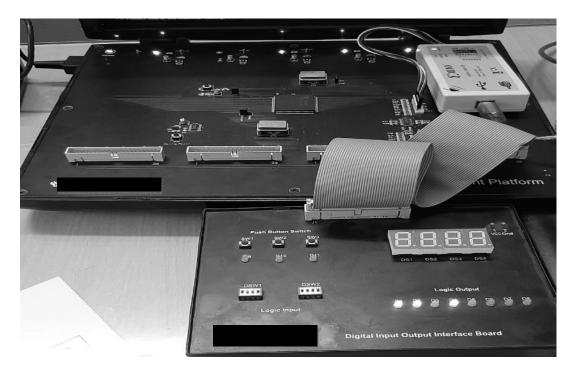

#### **FPGA Development board:**

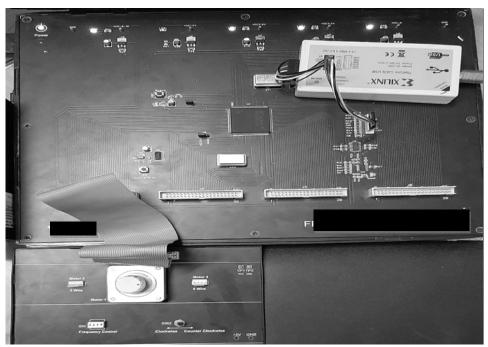

Fig 1.3 FPGA Development Board

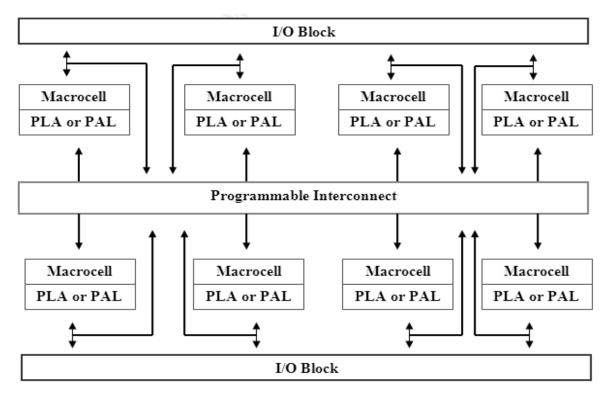

b) Complex Programmable Logic Device (CPLD): A Complex Programmable Logic Device (CPLD) is a combination of a fully programmable AND/OR array and a bank of macrocells. The AND/OR array is reprogrammable and can perform a multitude of logic functions. Macrocells are functional blocks that perform combinatorial or sequential logic, and also have the added flexibility for true or complement, along with varied feedback paths. Ref fig.. no. 1.4.

Fig 1.4 Block Diagram of CPLD

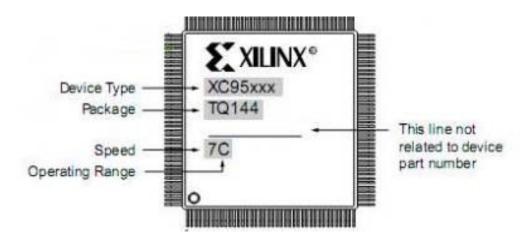

#### **Pin configuration of CPLD:**

Fig 1.5 Package Pinout Diagram

**Table no 1.2: General Pin Functions of CPLD IC**

| Sr. | Pin  | Functions                                                          |  |  |  |

|-----|------|--------------------------------------------------------------------|--|--|--|

| No  | name |                                                                    |  |  |  |

| 1.  | IO   | Each external I/O pin can be used as an input, an output, or a     |  |  |  |

|     | pins | bidirectional pin according to device programming. The I/O pins at |  |  |  |

|     |      | the bottom are also used for special purposes.                     |  |  |  |

| 2.  | GCK  | "Global Clocks" (GCK). Each macro cell can be programmed to        |  |  |  |

|    |     | use a selected clock input.                                           |

|----|-----|-----------------------------------------------------------------------|

| 3. | GSR | "Global Set/Reset" (GSR). Each macro cell can use this signal as an   |

|    |     | asynchronous Preset or Clear.                                         |

| 4. | GTS | "Global Three State Controls"                                         |

|    |     | (GTS).One of the signals can be selected in each macro cell to output |

|    |     | enable the corresponding output driver when the macro cell's output   |

|    |     | is hooked to an external I/O pin.                                     |

#### **CPLD Development Board:**

Fig1.6 CPLD Development Board

#### VIII Resources Required

| Sr.<br>No | Instrument /<br>Components | Specification                                                                                                                                                                                                                                     | Quantity |

|-----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.        | FPGA<br>Development<br>kit | Device: Xilinx FPGA (XC3S400 PQ208),On board +5V, +3.3V, +2.5V supply to FPGA and other hardware circuit., On board, 2 Crystal 8MHz and 25MHzJTAG Interface (Boundary Scan),PROM Interface (XCF02S),40 pin, 4 header connector for external I/O's | 1 No.    |

| Sr.<br>No | Instrument /<br>Components                | Specification                                                             | Quantity |

|-----------|-------------------------------------------|---------------------------------------------------------------------------|----------|

| 2.        | Desktop PC                                | Loaded with open source IDE, simulation and program downloading software. | 1 No.    |

| 3.        | Data Sheets of<br>Xilinx CPLD<br>and FPGA |                                                                           |          |

#### IX Precautions to be followed

- 1. Do not power up the development board when identifying the components on the board

- 2. Refer data sheets for the given development board.

#### X Resources Used

| Sr.<br>No. | Instrument /Components | Specification | Quantity |

|------------|------------------------|---------------|----------|

| 1.         |                        |               |          |

| 2.         |                        |               |          |

| 3.         |                        |               |          |

| XI | Precautions Followed (use blank sheet provided if space not sufficient) |

|----|-------------------------------------------------------------------------|

|    |                                                                         |

|    |                                                                         |

|    |                                                                         |

|    |                                                                         |

|    |                                                                         |

|    |                                                                         |

|    |                                                                         |

## **XII Observations** (use blank sheet provided if space not sufficient) Observe the pin out diagram for FPGA and give the functions of following pins:

| Sr No | Pins | Functions |

|-------|------|-----------|

| 1.    | JTAG |           |

| 2.    | DCI  |           |

| 3.    | DUAL |           |

| 4.    | VCCO |           |

| 5.    | GCLK |           |

| XIII  | Conclusion and Recommendation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| XIV   | <ul> <li>Practical Related Questions</li> <li>Note: Below given are few sample questions for reference. Teacher must design more such questions so as to ensure the achievement of identified CO</li> <li>1. List the features of FPGA.</li> <li>2. List the features of CPLD.</li> <li>3. Compare FPGA and CPLD on the basis of following points: <ul> <li>a. Power consumption.</li> <li>b. Number of input and output pins.</li> <li>c. Complexity in board design and layout.</li> <li>d. Prediction of speed performance of design.</li> </ul> </li> </ul> |  |  |  |  |  |

|       | [Space for Answers]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Very Large Scale Integration with VHDL (22062) |

|------------------------------------------------|

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

#### XV References / Suggestions for further reading

- 1 http://www.ti.com/lit/ds/symlink/ads1258-ep.pdf

- 2 http://www.datasheetdir.com/ADS1258+24bit-Analog-Digital-Converter

- 3 http://www.datasheetdir.com/CPLD

- 4 https://www.dataman.com/media/datasheet/Atmel/ATF1502ASV\_doc1615.pdf

#### XVI Assessment Scheme

|                            | Performance indicators Weightage                        |      |  |

|----------------------------|---------------------------------------------------------|------|--|

|                            | Process related (15 Marks)                              | 60%  |  |

| 1                          | Identifying the development board                       | 30%  |  |

| 2                          | Identifying components on developer kit                 | 20%  |  |

| 3                          | Follow ethical practices.                               | 10%  |  |

| Product related (10 Marks) |                                                         |      |  |

| 4                          | Correct pin functions                                   | 20%  |  |

| 5                          | Answer to sample questions.                             | 15%  |  |

| 6                          | Timely Submission of report Answer to sample questions. | 05%  |  |

|                            | TOTAL (25 Marks)                                        | 100% |  |

#### Name of student Team Member

| 1. | <br> |  |

|----|------|--|

| 2. | <br> |  |

| 3. | <br> |  |

| 1  |      |  |

| Marks Obtained             |                            |            |                            |

|----------------------------|----------------------------|------------|----------------------------|

| Process<br>Related<br>(15) | Product<br>Related<br>(10) | Total (25) | Dated signature of Teacher |

|                            |                            |            |                            |

#### Practical No. 02: Develop flowchart of CMOS IC fabrication using relevant website.

#### I Practical Significance

Complementary metal—oxide—semiconductor (CMOS) is a type of MOSFET (metal—semiconductor field-effect transistor) semiconductor device fabrication process used for constructing integrated circuits (ICs). CMOS technology is used in microprocessors, microcontrollers, memory chips, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. This practical will help the student to understand the CMOS IC fabrication process.

#### II Relevant Program Outcomes (POs)

- Discipline knowledge: Apply Electronics and Telecommunication engineering knowledge to solve broad-based Electronics and Telecommunications engineering related problems.

- **Experiments and practice:** Plan to perform experiments and practices to use the results to solve broad-based Electronics and Telecommunication engineering problems.

- **Engineering tools:** Apply relevant Electronics and Telecommunications technologies and tools with an understanding of the limitations.

- **Lifelong learning:** Engage in independent and life-long learning activities in the context of technological changes also in the Electronics and Telecommunication engineering and allied industry

#### III Competency and Practical Skills

This practical is expected to develop the following skills for the industry-identified competency: 'Maintain VLSI based electronic circuits and equipments.''

- Understand the CMOS IC fabrication.

- To develop the flowchart for CMOS fabrication.

#### **IV** Relevant Course Outcome

Interpret CMOS technology circuits with their specifications.

#### V Practical Outcome

Develop flowchart of CMOS IC fabrication using relevant website.

#### VI Relevant Affective domain related Outcome(s)

- Follow safety practices.

- Maintain tools and equipment.

- Follow ethical practices.

#### VII Minimum Theoretical Background

For less power dissipation requirement CMOS technology is used for implementing transistors. If we require a faster circuit then transistors are implemented over IC using BJT. Fabrication of CMOS transistors as IC's can be done in three different methods.

• The N-well / P-well technology, where n-type diffusion is done over a p-type substrate or p-type diffusion is done over n-type substrate respectively.

• The Twin well technology, where NMOS and PMOS transistor are developed over the wafer by simultaneous diffusion over an epitaxial growth base, rather than a substrate.

The silicon On Insulator process, where rather than using silicon as the substrate an insulator material is used to improve speed and latch-up susceptibility.

#### **MOS Fabrication Steps:**

The CMOS fabrication process flow is conducted using following basic fabrication steps while manufactured using N- well/P-well technology.

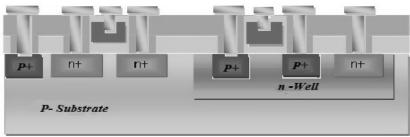

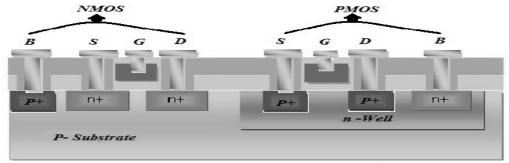

#### Making of CMOS using N well

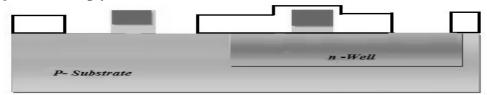

**Step 1:** First we choose a substrate as a base for fabrication. For N- well, a P-type silicon substrate is selected.

Fig 2.1: Selection of Substrate

**Step 2 – Oxidation:** The selective diffusion of n-type impurities is accomplished using SiO2 as a barrier which protects portions of the wafer against contamination of the substrate. SiO<sub>2</sub> is laid out by oxidation process done exposing the substrate to high-quality oxygen and hydrogen in an oxidation chamber at approximately  $1000^{0}$ c

Fig 2.2: Oxidation

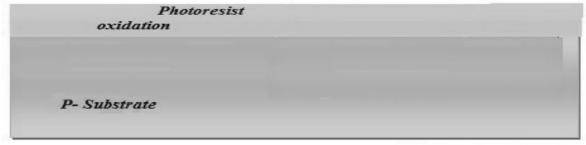

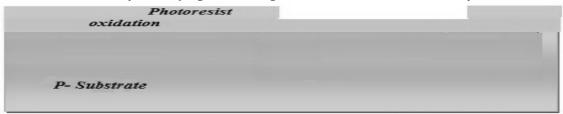

**Step 3 – Growing of Photoresist:** At this stage to permit the selective etching, the SiO2 layer is subjected to the photolithography process. In this process, the wafer is coated with a uniform film of a photosensitive emulsion.

Fig 2.3: Growing of Photoresist

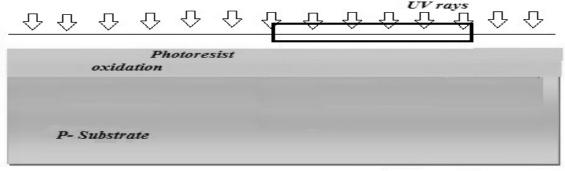

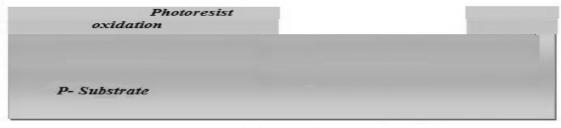

**Step 4 – Masking:** This step is the continuation of the photolithography process. In this step, a desired pattern of openness is made using a stencil. This stencil is used as a mask over the photoresist. The substrate is now exposed to **UV rays** the photoresist present under the exposed regions of mask gets polymerized.

Fig 2.4: Masking

**Step 5 – Removal of Unexposed Photoresist:** The mask is removed and the unexposed region of photoresist is dissolved by developing wafer using a chemical such as Trichloroethylene.

Fig 2.5: Removal of Unexposed Photoresist

**Step 6** – **Etching:** The wafer is immersed in an etching solution of hydrofluoric acid, which removes the oxide from the areas through which dopants are to be diffused.

Fig 2.6: Etching

Step 7 – Removal of Whole Photoresist Layer: During the etching process, those portions of SiO2 which are protected by the photoresist layer are not affected. The photoresist mask is now stripped off with a chemical solvent (hot H2SO4).

Fig 2.7: Removal of Photoresist Layer

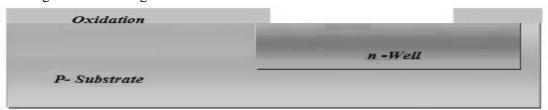

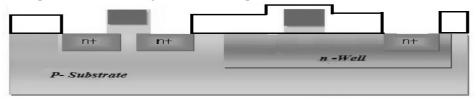

**Step 8 – Formation of N-well:** The n-type impurities are diffused into the p-type substrate through the exposed region thus forming an N- well.

Fig 2.8: Formation of N-Well

**Step 9 – Removal of SiO2:** The layer of SiO2 is now removed by using hydrofluoric acid.

Fig 2.9: SiO2 Removal of SiO2

**Step 10 – Deposition of Polysilicon:** The misalignment of the gate of a **CMOS transistor** would lead to the unwanted capacitance which could harm circuit. So to prevent this "Self-aligned gate process" is preferred where gate regions are formed before the formation of source and drain using ion implantation.

Fig 2.10: Polysilicon Deposition

Polysilicon is used for formation of the gate because it can withstand the high temperature greater than 8000°c when a wafer is subjected to annealing methods for formation of source and drain. Polysilicon is deposited by using **Chemical Deposition Process** over a thin layer of gate oxide. This thin gate oxide under the Polysilicon layer prevents further doping under the gate region.

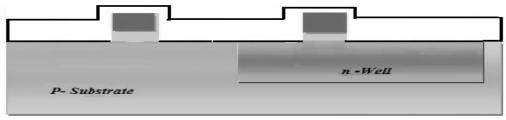

**Step 11 – Formation of Gate Region:** Except the two regions required for formation of the gate for **NMOS and PMOS transistors** the remaining portion of Polysilicon is stripped off.

Fig 2.11: Formation of Gate Region

**Step 12** – **Oxidation Process:** An oxidation layer is deposited over the wafer which acts as a shield for further **diffusion and metallization processes**.

Fig 2.12: Oxidation Process

**Step 13 – Masking and Diffusion:** For making regions for diffusion of n-type impurities using masking process small gaps are made.

Fig 2.13.a: Masking and Diffusion

Using diffusion process three n+ regions are developed for the formation of terminals of NMOS.

Fig 2.13.b: Masking and Diffusion

**Step 14 – Removal of Oxide:** The oxide layer is stripped off.

Fig 2.14: Removal of Oxide

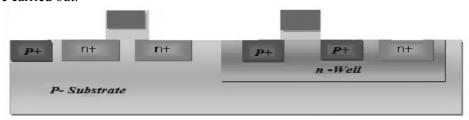

**Step 15 – P-type Diffusion:** Similar to the n-type diffusion for forming the terminals of PMOS p-type diffusion are carried out.

Fig 2.15: P-Type Diffusion

**Step 16 – Laying of Thick Field oxide:** Before forming the metal terminals a thick field oxide is laid out to form a protective layer for the regions of the wafer where no terminals are required.

Fig 2.16: Laying of Thick Oxide

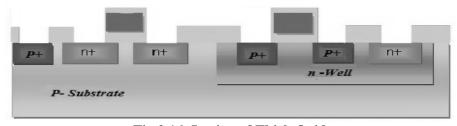

**Step 17 – Metallization:** This step is used for the formation of metal terminals which can provide interconnections. Aluminum is spread on the whole wafer.

Fig 2.17: Metallization

**Step 18 – Removal of Excess Metal:** The excess metal is removed from the wafer.

**Step 19 – Formation of Terminals:** In the gaps formed after removal of excess metal terminals are formed for the interconnections.

Fig 2.18: Terminal Formation

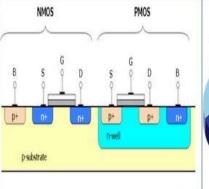

Step 20 – Assigning the Terminal Names: Names are assigned to the terminals of NMOS and PMOS transistors.

Fig 2.19: Terminal Naming

**VIII Observations** (use blank sheet provided if space not sufficient)

Draw the flowchart for the CMOS IC fabrication using N well Process.

| IX    | Conclusion and Recommendation                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| X     | <ul> <li>Practical Related Questions</li> <li>Note: Below given are few sample questions for reference. Teacher must design more such questions so as to ensure the achievement of identified CO</li> <li>1. List the CMOS applications.</li> <li>2. Draw the process diagram of CMOS Fabrication using P well process.</li> <li>3. Draw the flowchart for the CMOS fabrication using Twin tub process.</li> </ul> |

|       | [Space for Answers]                                                                                                                                                                                                                                                                                                                                                                                                |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ••••• |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Very Large Scale Integration with VHDL (22062) |

|------------------------------------------------|

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

|                                                |

#### XI References / Suggestions for further reading

- 1 https://www.elprocus.com/the-fabrication-process-of-cmos-transistor/

- 2 https://www.slideshare.net/cmos-fabrication

- 3 https://www.electronics-tutorial.net/CMOS-Processing-Technology/Twin-tub-Process/

#### XII Assessment Scheme

|   | Performance indicators Weightage                        |      |  |

|---|---------------------------------------------------------|------|--|

|   | Process related (15 Marks)                              | 60%  |  |

| 1 | Identifying the fabrication process                     | 30%  |  |

| 2 | Listing the steps in fabrication process.               | 20%  |  |

| 3 | Follow ethical practices. 10%                           |      |  |

|   | 40%                                                     |      |  |

| 4 | Correct material selection                              | 20%  |  |

| 5 | 5 Answer to sample questions.                           |      |  |

| 6 | Timely Submission of report Answer to sample questions. | 05%  |  |

|   | Total (25 Marks)                                        | 100% |  |

#### Name of student Team Member

| 1. |  |

|----|--|

| 2. |  |

| 3. |  |

| 4. |  |

| Marks Obtained             |                            |            |                            |

|----------------------------|----------------------------|------------|----------------------------|

| Process<br>Related<br>(15) | Product<br>Related<br>(10) | Total (25) | Dated signature of Teacher |

|                            |                            |            |                            |

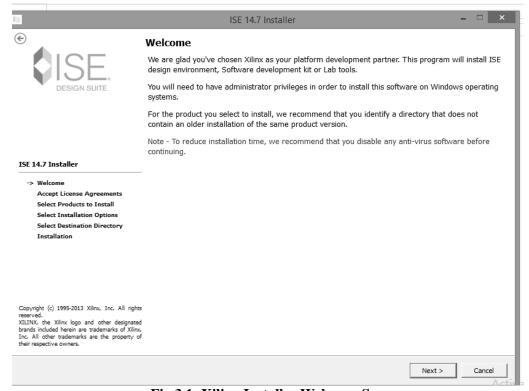

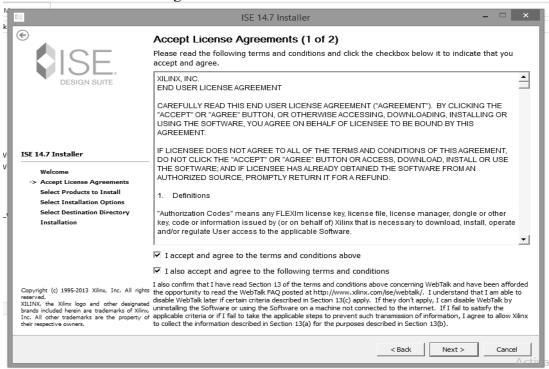

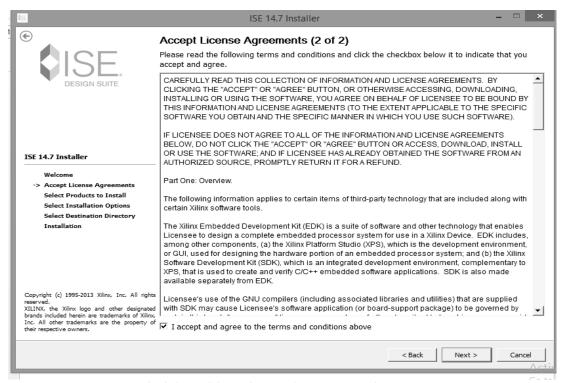

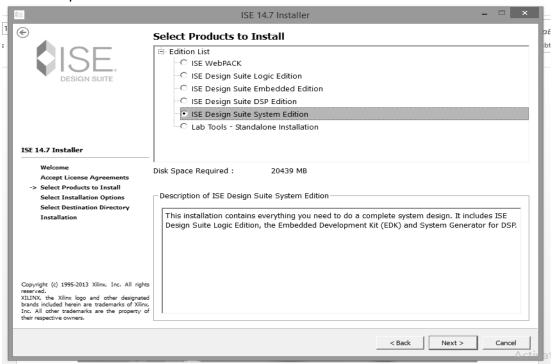

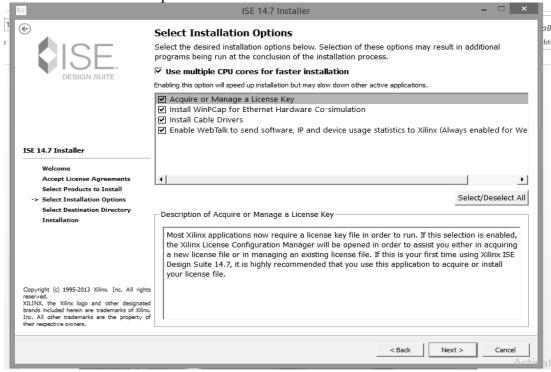

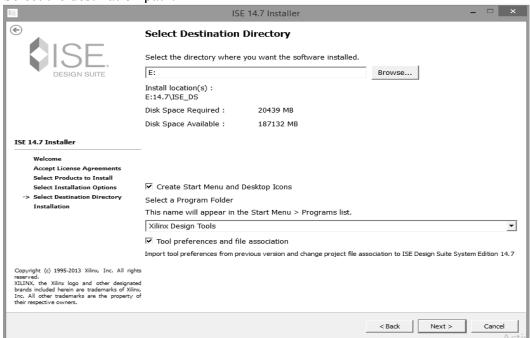

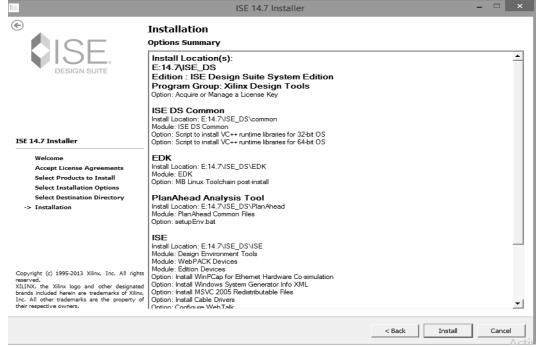

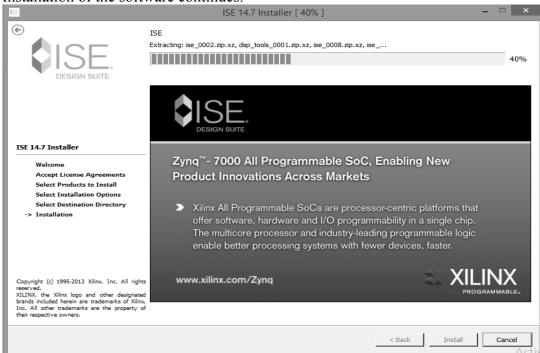

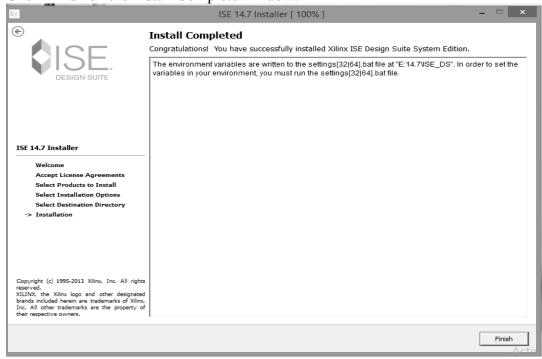

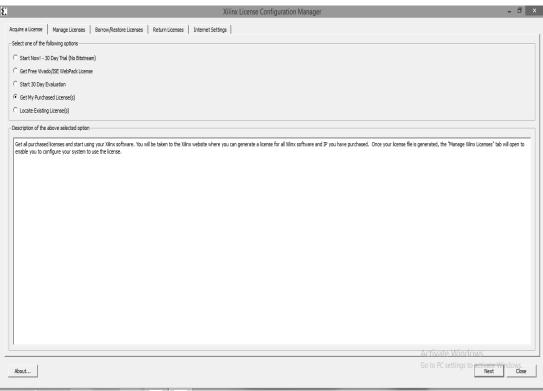

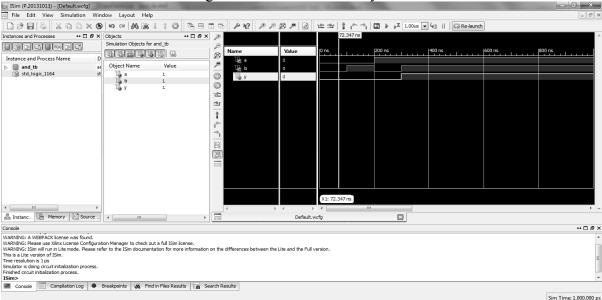

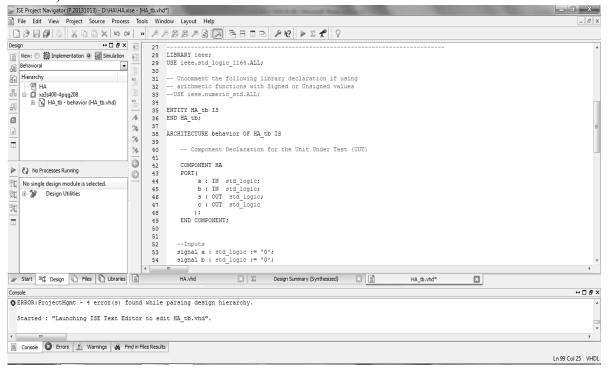

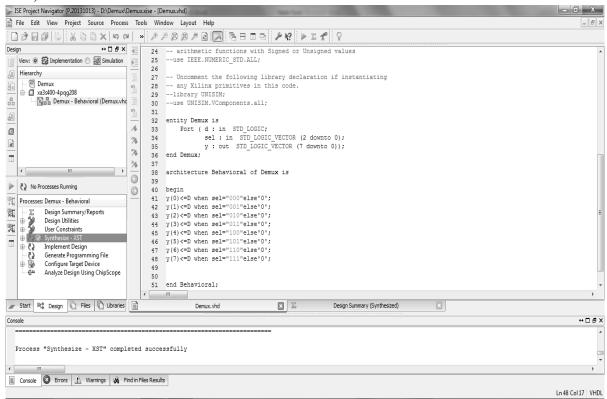

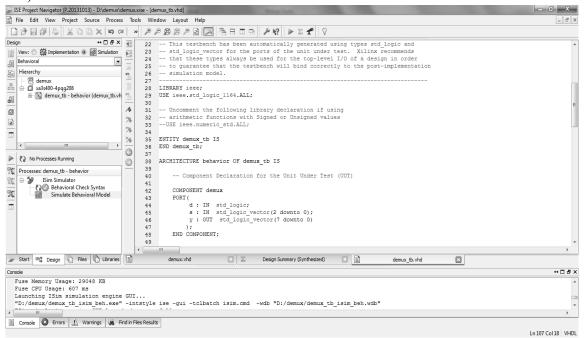

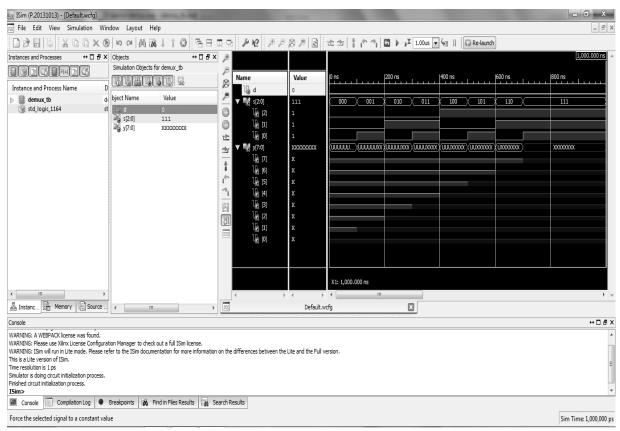

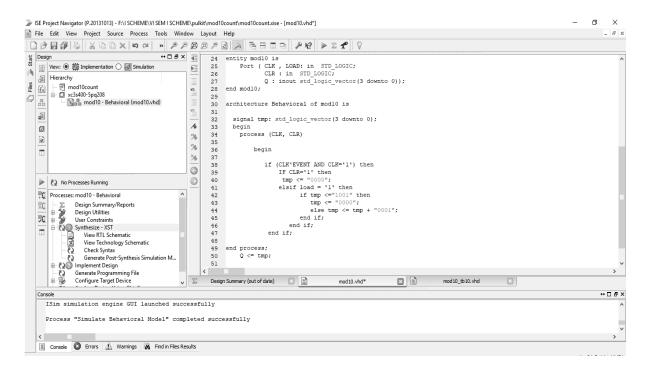

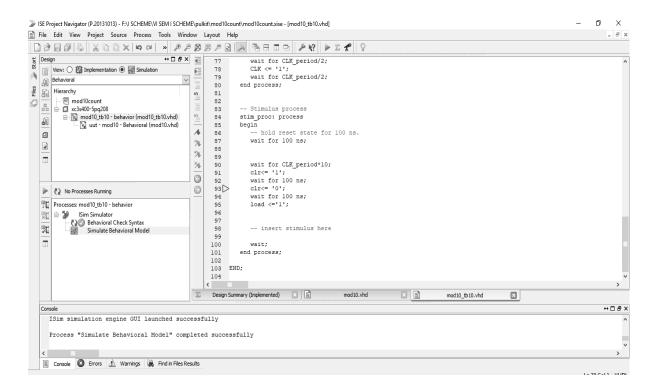

#### Practical No. 03: Install EDA tool for VLSI application.

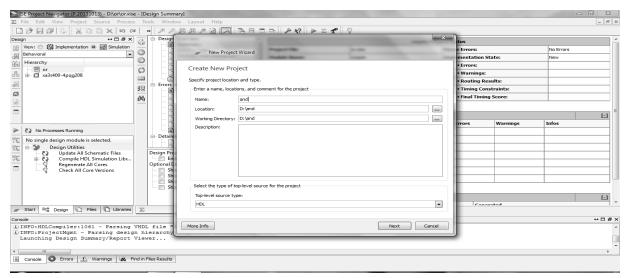

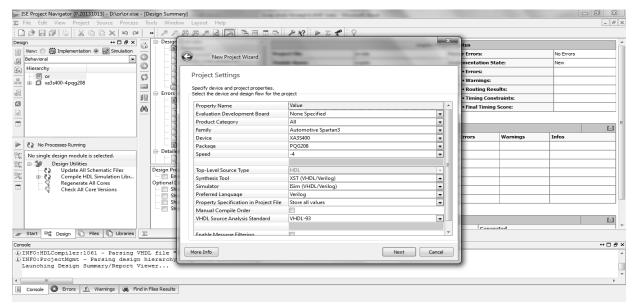

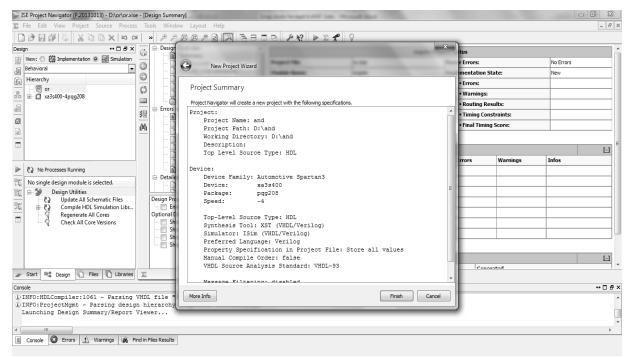

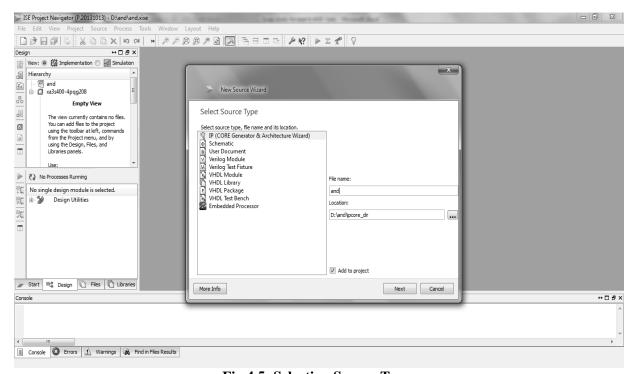

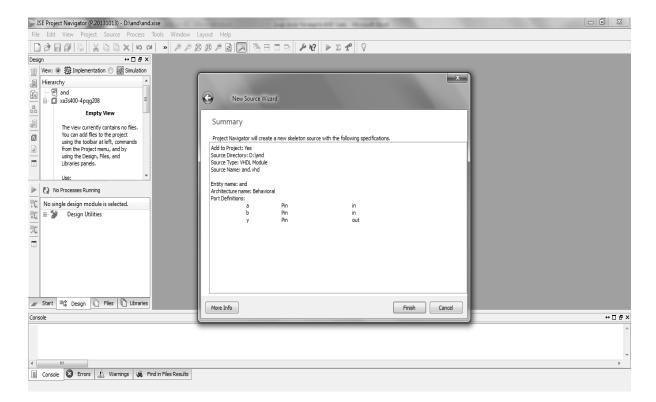

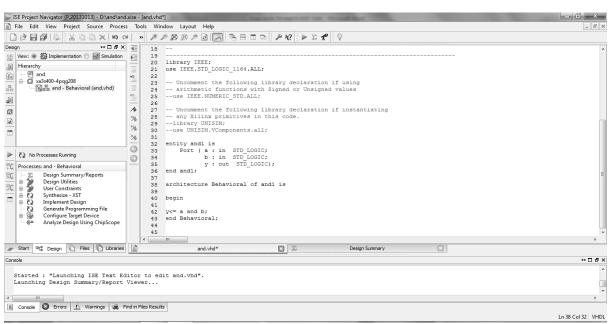

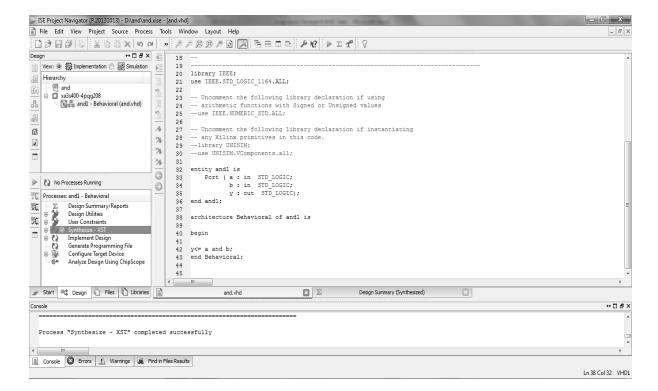

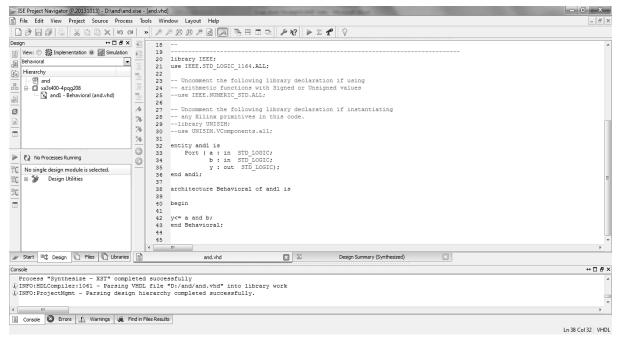

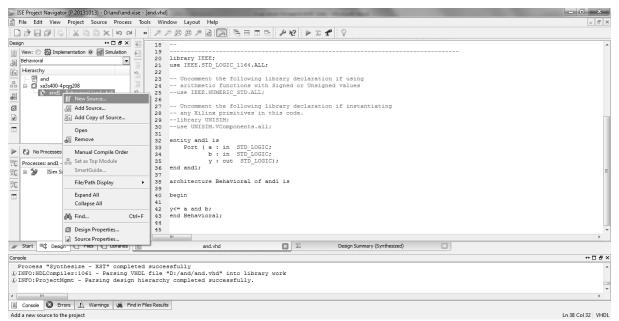

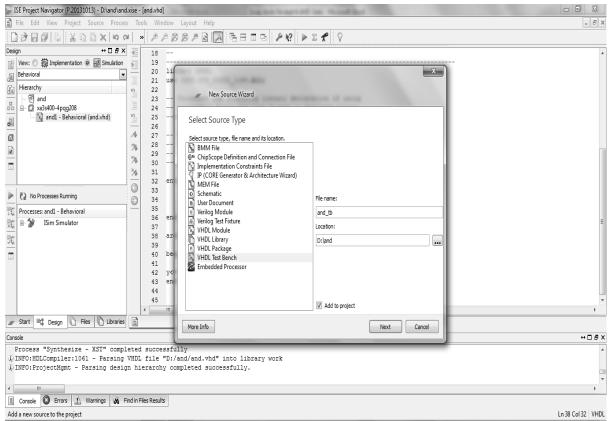

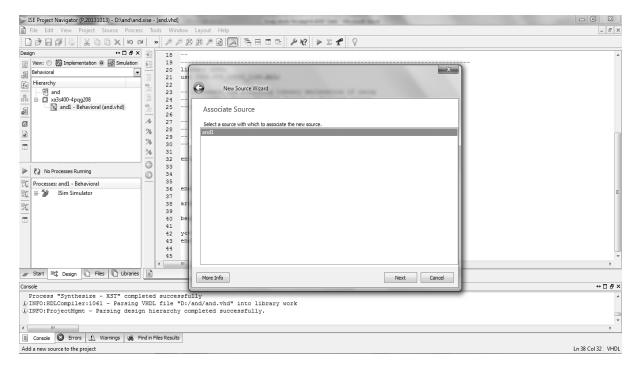

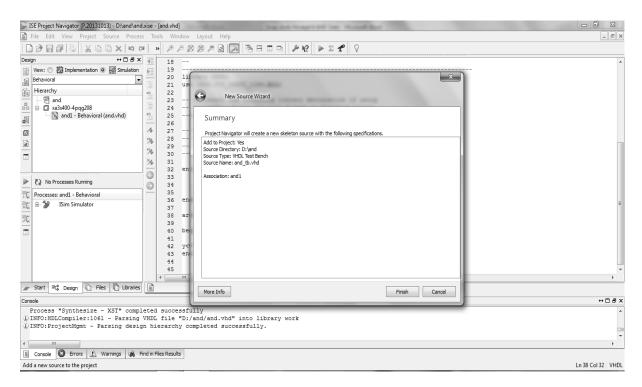

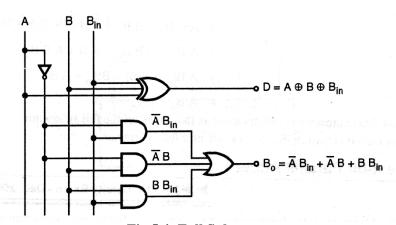

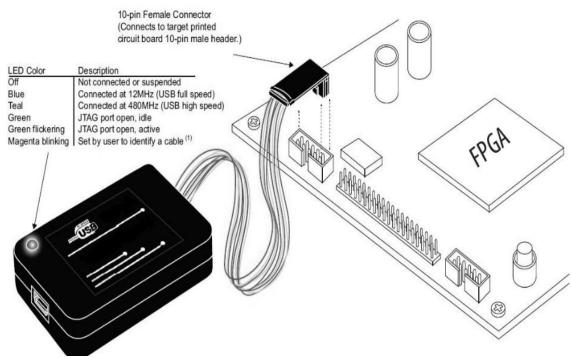

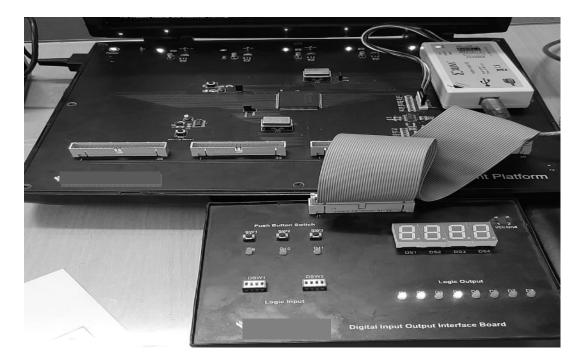

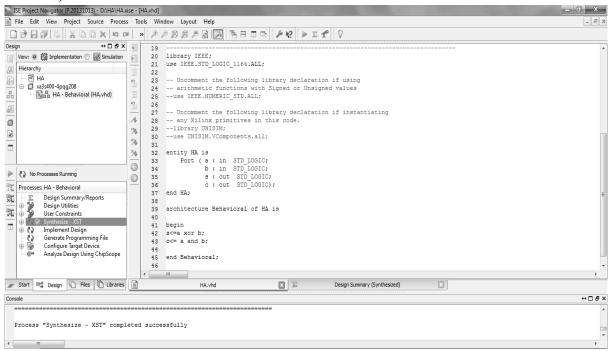

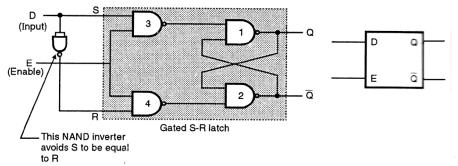

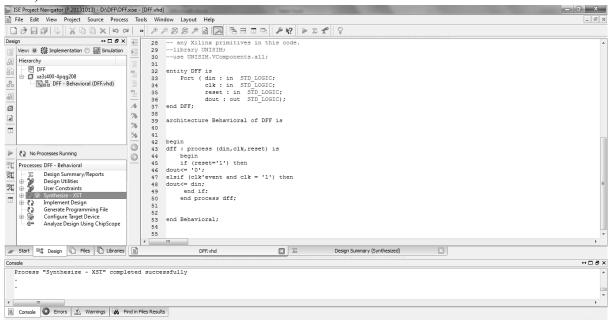

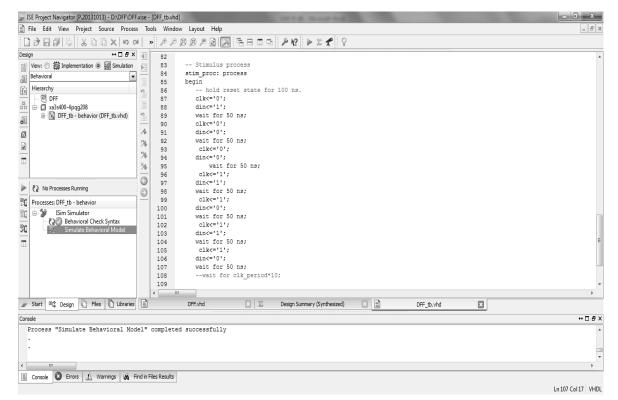

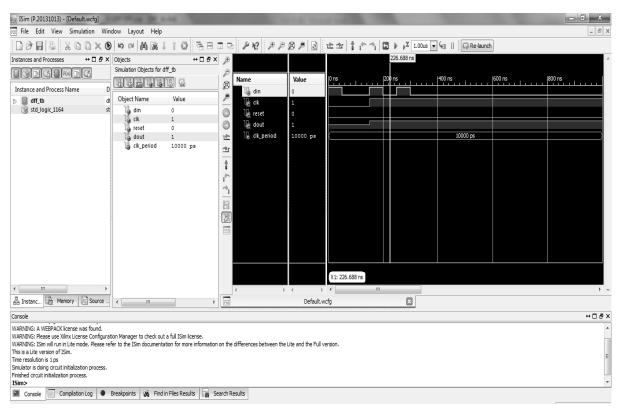

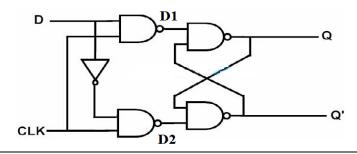

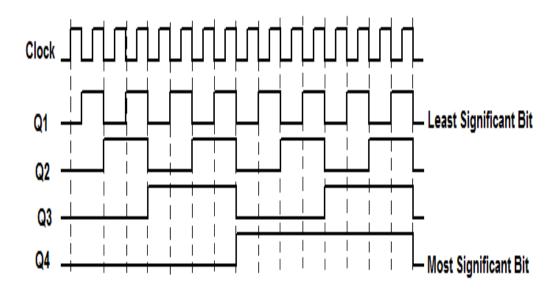

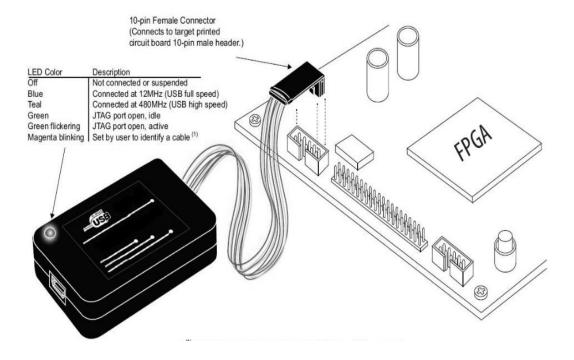

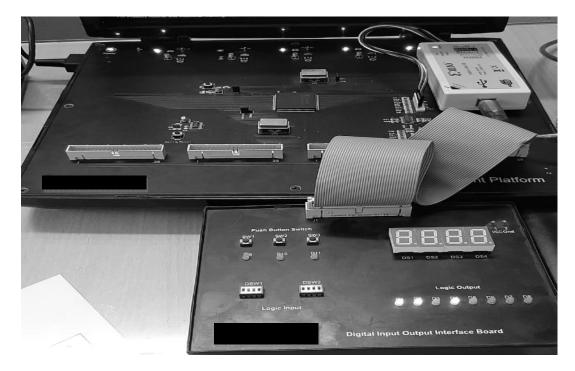

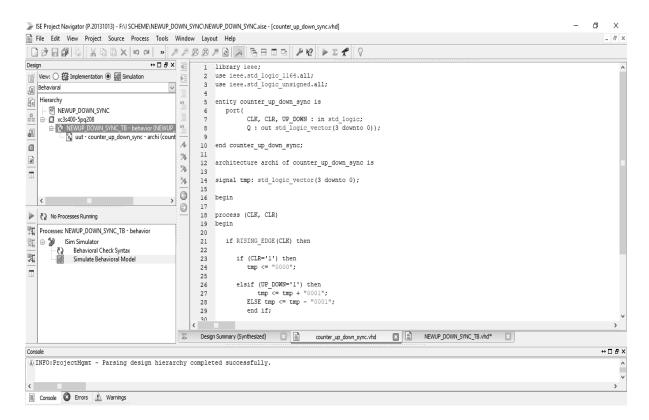

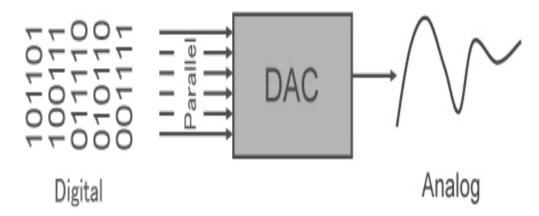

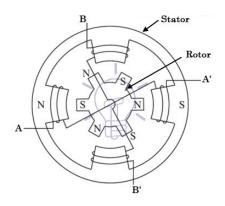

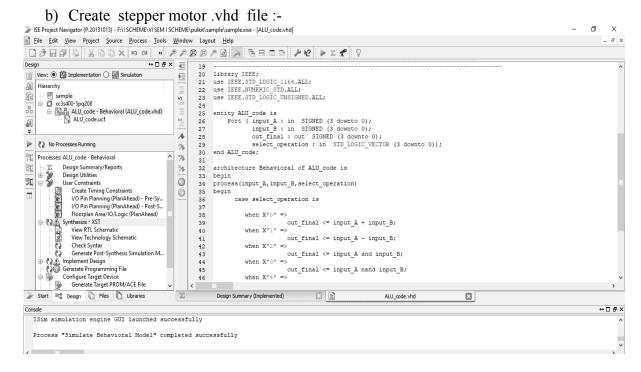

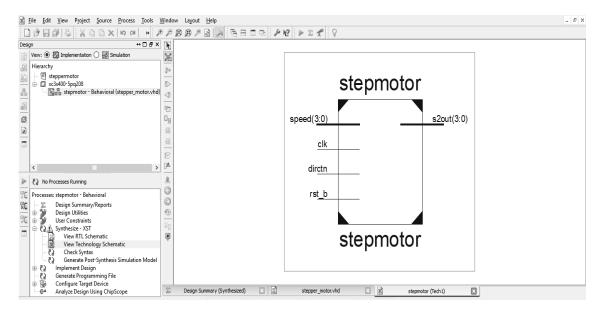

#### I Practical Significance